2. 中国科学院机器人与智能制造创新研究院, 辽宁 沈阳 110016;

3. 中国科学院大学, 北京 100049

2. Institutes for Robotics and Intelligent Manufacturing, Chinese Academy of Sciences, Shenyang 110016, China;

3. University of Chinese Academy of Sciences, Beijing 100049, China

0 引言

WIA-PA(wireless networks for industrial automation process automation,面向工业过程自动化的工业无线网络标准技术)标准[1]是中国工业无线联盟针对过程自动化领域制定的WIA子标准,是基于IEEE 802.15.4标准[2]的用于工业过程测量、监视与控制的无线网络通信规范.无线传感器网络的一个重要特征就是能量受限[3],采用WIA-PA标准的无线变送器一般部署在环境恶劣的工业环境下,通常无法提供电源供电,故多采用电池供电. WIA-PA系统级芯片是WIA-PA现场设备的核心组件,除了实现WIA-PA标准功能外,还负责对数据采集、模拟/数字量输入/输出、静态数据存储器等非核心模块进行管理,其中也包含对这些非核心模块的电源管理. WIA-PA系统级芯片的功耗在WIA-PA现场设备的整体功耗中占有较大的比重.综上,对面向WIA-PA系统级芯片的低功耗设计方法进行研究具有重要意义和应用价值.

系统级芯片的低功耗设计一直是大规模集成电路设计领域的热点和难点.嵌入式系统级芯片常用的低功耗设计方法包括减少电路翻转、关断待机电路、系统级优化等[4].芯片的电源消耗可划分为2类:一类是动态功耗,在芯片活动状态下生成;另一类是静态功耗,在芯片任何工作状态下都会生成.对于动态功耗,通常采用时钟门控[5]或动态电压频率调整技术[6-7]来实现低功耗.在动态电压频率调整基础上,对待机模块关断电源可以达到更好的低功耗优化效果[8].对于静态功耗,对工艺库进行优化修改是最有效的办法,工艺库的改进可以通过直接优化MOS(metal oxide semiconductor,金属氧化物半导体)工艺器件实现[9].此外,为了降低静态功耗,新型的半导体材料也越来越被关注并用于器件的制造[10-11].除了以直接降低动态/静态功耗为目的的寄存器级低功耗优化方法以外,在系统级层面进行功耗优化,也是较为有效的方法,如将常用的功能设计为专用的硬件单元,替代对处理器资源的使用[12],根据算法优化系统布局实现从基本处理单元到资源结点的映射[13].采用异步电路进行数字电路设计也是低功耗设计的一种常用手段[14].此外,芯片在工作/休眠状态下自动进行主电源供电和低漏电电源供电切换[15]也是实现低功耗优化的另一种可行方法.

针对WIA-PA系统级芯片的功耗优化需要从2个方面考虑:一是应用场景,由于WIA-PA系统级芯片采用电池供电,需要同时对静态功耗与动态功耗进行优化,这与大多数系统级芯片只需要对动态/静态功耗其中之一作为优化目标有所不同;二是电路结构,WIA-PA系统芯片分为模拟电路和数字电路两部分,其中模拟电路包含射频前端电路、稳压电路、RC振荡电路、上电复位电路等;数字电路包括处理器、基带电路、常用外设等,复杂的电路类型需要在同一硅片上完成生产制造,对工艺制程的兼容性要求十分严格,使得可选的工艺制程具有很大的限定性,进而限制了针对工艺的功耗优化方法,因此WIA-PA系统级芯片必须综合使用时钟门控[5]、减少电路翻转、关断待机电路、系统级优化等[4]多种技术.此外,采用新型半导体材料实现低功耗[10-11]目前还处于理论研究或实验室阶段,具有工艺兼容性差、尚未在大规模集成电路上应用等缺点,本文不予采用;直接修改MOS工艺器件的方法需要经过多轮的流片验证、测试,研发周期长,也不适用于WIA-PA系统级芯片.

针对上述问题,本文提出一种面向WIA-PA系统级芯片的低功耗优化策略,综合采用门控时钟、异步电路、主/低漏电电源切换、电源管理模块、系统级优化、多种工艺库对比等方法,最终达到对静态功耗和动态功耗两者共同优化的目的.

1 概述 1.1 WIA-PA设备功耗分析WIA-PA标准使用超帧组织网络资源.超帧是一组重复出现的时隙序列组合,以时隙成员数量为周期,用于对时隙资源进行组织和管理. WIA-PA标准工业无线网络通常包括网关、路由设备和现场设备.网关与路由设备构成Mesh网络,路由设备与现场设备组成星形网络.在WIA-PA应用中,网关和路由设备一般采用电源供电;现场设备多采用电池供电.因此,采用电池供电的现场设备是低功耗优化的重点考虑对象.

支持WIA-PA标准的常用芯片有CC2420[16]、CC2530(8051)[17]、CC2538(CM3)[18]、JN516x[19]、MKW2xD(CM4)[20]、EM351/EM357[21]等,对这些芯片的空闲、发射、接收状态下的功耗进行统计,并对不同状态下的统计值计算平均值作为2.4 GHz系统级芯片在各状态下的功耗. WIA-PA现场设备在工作周期可分为活动状态和休眠状态. WIA-PA现场设备在入网时可分为侦听、接收和发送三个状态;在接收/发送时隙内,可分为微控制器(MCU)活动状态、侦听状态、发射状态、接收状态;在非时隙内,为休眠状态.归纳可得出WIA-PA系统级芯片的活动状态包括MCU活动状态、侦听状态、发射状态和接收状态,非活动状态也就等效于休眠状态. WIA-PA活动状态发生在设备加入、接收时隙和发送时隙的过程中;休眠状态发生在设备的非时隙过程中.目前WIA-PA标准已经在多个领域得到了应用,通过对WIA-PA现场设备在油田采油监测与优化分析现场应用的组网参数及入网参数进行统计并作为参照,WIA-PA现场设备在网运行时的主要参数给定值见表 1.

| WIA-PA系统级芯片工作状态 | 符号 | 参数值 |

| 休眠状态电流(sleeptime) | Isleep | 13 μA |

| MCU活动状态电流* | Imcu | 14 mA |

| 侦听状态电流** | Ilisten | 26 mA |

| 发射状态电流** | Itx | 37 mA |

| 接收状态电流** | Irx | 35 mA |

| 设备加入时间 | tadd | 90 s |

| 设备加入过程侦听时间 | tadd_listen | 75 s |

| 设备加入过程接收时间 | tadd_rx | 12 s |

| 设备加入过程发送时间 | tadd_tx | 3 s |

| 设备断网/重新加入周期 | tadd_cycle | 7 d |

| 超帧周期 | tsuperframe | 32 s |

| 时隙周期 | tslot | 15.625 ms |

| 设备接收时隙平均侦听时间 | trx_listen | 192 μs |

| 设备接收时隙平均接收时间 | trx_rx | 1 024 μs |

| 设备接收时隙平均发送时间 | trx_tx | 384 μs |

| 设备接收时隙射频空闲时间 | trx_idle | 14.025 ms |

| 设备发射时隙平均侦听时间 | ttx_listem | 144 μs |

| 设备发射时隙平均接收时间 | ttx_rx | 576 μs |

| 设备发射时隙平均发送时间 | ttx_tx | 768 μs |

| 设备发射时隙射频空闲时间 | ttx_idle | 14.137 ms |

| 注:*表示WIA-PA系统级芯片在MCU活动,RF等其它模块休眠状态下的功耗;**表示WIA-PA系统级芯片在MCU、RF活动下的功耗. | ||

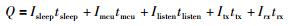

用Q表示WIA-PA系统级芯片的电池耗电量,计算方法为电流乘以时间,单位为mAh.对于WIA-PA系统级芯片,耗电量Q的计算公式为

|

(1) |

式中,tsleep表示休眠总时间,包括在接收、发送时隙时的休眠时间和在非时隙过程中的休眠时间;tmcu表示MCU工作总时间,指在整个工作周期内所有接收、发送时隙过程的空闲时间中MCU的活动时间的和;tlisten表示侦听总时间,指在整个工作周期内所有接收、发送时隙过程中侦听时间的和;ttx表示发送总时间,指在所有状态下发送时间的和;trx表示接收总时间,指在所有状态下接收时间的和.在接收、发送空闲时隙时间内,近似以其60%为MCU活动状态时间,40%为休眠状态时间.

根据WIA-PA标准中超帧的运行特点,WIA-PA现场设备以运行1 y为周期,不同状态运行时间计算结果见表 2,在计算的过程中假设设备处于工作时隙空闲时间内.将表 1芯片在不同状态下的功耗与表 2在不同状态下的工作时间代入式(1),可计算出WIA-PA系统芯片在1年工作周期中,在不同状态下的耗电量,其中活动状态消耗电量为130.07 mAh,占总耗电量的比例为53.3%;休眠状态耗电量为113.79 mAh,占总耗电量的比例为46.7%.

| WIA-PA系统级芯片状态工作时间 | 符号 | 时间 |

| 休眠总时间 | tsleep | 8 753.226 h |

| MCU活动总时间 | tmcu | 4.625 h |

| 侦听总时间 | tlisten | 1.178 h |

| 发送总时间 | ttx | 0.359 h |

| 接收总时间 | trx | 0.612 h |

由结果可知,WIA-PA系统级芯片在整个工作周期内,活动状态与休眠状态下消耗的电量的比例接近于1比1,所以对WIA-PA系统级芯片的功耗进行优化需从动态功耗和静态功耗两个方面入手.

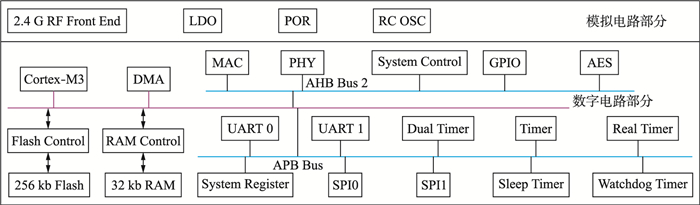

1.2 WIA-PA系统级芯片系统结构WIA-PA系统级芯片是一款基于ARM Cortex-M3内核、集成2.4 GHz无线通信模块的32位系统级芯片,其结构框如图 1所示.该芯片采用QFN56封装,集成了32 kb RAM和256 kb Flash,系统时钟最高频率可达32 MHz.具有GPIO、UART、SPI、DMA、定时器等通用模块,可以作为通用处理器使用. 2.4 GHz无线通信模块符合WIA-PA标准,可以满足工业无线传感器网络的数据处理和通信要求.相对比于其它常用的无线芯片,WIA-PA系统级芯片集成了支持WIA-PA标准的MAC层硬件状态机和符合CCM*模式安全规范的AES-128硬件加/解密安全模块.

|

| 图 1 WIA-PA系统级芯片结构框图 Figure 1 Block diagram of the WIA-PA SoC structure |

WIA-PA系统级芯片按照电路类型、可分为模拟电路部分和数字电路部分两个部分.其中,模拟系统包含射频前端、低压差线性稳压器(low dropout regulator,LDO)、上电复位(power on reset,POR)、RC振荡器等;数字系统包括处理器、基带MAC模块、DMA控制器、AES加解密模块、串口、定时器等外设模块.

1.3 WIA-PA系统级芯片低功耗优化策略满足在有限能源前提下可长时间工作是WIA-PA现场设备的一个基本需求,因此对于WIA-PA系统级芯片的技术研究和设计开发,除了实时性、可靠性和安全性等要求之后,功耗是衡量芯片是否成功的重要考核指标.如果功耗指标不满足要求,将导致WIA-PA系统级芯片在电池供电条件下的应用具有连续工作时间短,维护成本高等问题,市场竞争力下降.综上所述,WIA-PA系统级芯片只有经过全面的低功耗优化才能满足有限电池容量下的应用需求.

WIA-PA系统级芯片的低功耗设计需要从系统级、寄存器传输级到逻辑门电路级进行全面考虑. WIA-PA系统级芯片的低功耗设计采用全面的优化策略,依不同设计层次采用不同的优化方法.系统供电方面,采用具有电路简单、低功耗和低压差等特点的LDO[22]进行供电,并在活动/休眠模式状态下分别使用大驱动能力的LDO和低功耗的LDO.双LDO切换可以避免在休眠状态下大驱动能力LDO的漏电,可有效降低静态功耗.在系统级层面,设计合理的系统架构、灵活的时钟分配、双LDO切换结构及多种工作模式.合理的系统架构设计可以保证总线分布合理,灵活的时钟分配保证时钟管理的最优化,这两种优化方法都可以避免多余的模块使用和寄存器翻转,可有效降低动态功耗.芯片的多种工作模式对应在不同场景下的资源需求.在寄存器级层面,从主动设计和工具优化两个方面进行时钟门控.在门级电路优化层次,先进的低功耗制造工艺是降低芯片功耗的捷径.上述低功耗优化方法与设计层次的对应关系可归纳为表 3.

| 设计层次 | 优化方法 |

| 系统级优化 | 系统架构设计 |

| 灵活时钟分配 | |

| 多种工作模式 | |

| WIA-PA硬件加速引擎 | |

| LDO/LP-LDO切换 | |

| 电源管理单元 | |

| 寄存器级功耗优化 | 时钟门控 |

| RTL代码优化 | |

| 门级优化 | 低功耗工艺库 |

WIA-PA系统级芯片综合采用了多种优化方法,但这些优化方法并不是孤立的,而是彼此联系的.在时钟优化方面,根据不同模块的工作特点,选用不同的时钟源及时钟控制策略.供电部分采用了双LDO的切换方法.在传统的实现方式中,WIA-PA协议处理是一项重复频次很高的处理器任务,占用了大量的CPU时间,所以设计了面向WIA-PA优化的协议加速器来代替传统的实现方式.不同的时钟配置和LDO选择可以组合出多种工作模式,复杂的工作模式增加了芯片的逻辑资源,因此需要根据在WIA-PA标准不同的工作场景选择适合的工作模式.工作模式提供了在不同应用场景下的硬件资源划分方法,电源管理单元则是实现在不同工作模式下的资源调度的硬件模块.电源管理单元统一管理时钟、LDO等资源,根据不同的需求,生成不同的时钟、LDO控制信号,实现对应的工作模式.工艺制程的选择也是最终芯片功耗指标的重要影响因素.

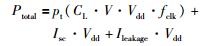

2.1 时钟优化设计 2.1.1 时钟源数字集成电路的功耗主要由3个部分组成[23],可以归纳表示为

|

(2) |

式中,等号右边的第1项是开关功耗,其中CL表示负载电容,fclk表示时钟频率,pt表示寄存器翻转的概率,通常情况下,电压摆幅V和电源电压Vdd相等;第2项是短路电流功耗,其中Isc表示当PMOS(positive channel metal oxide semiconductor,P沟道金属氧化物半导体)和NMOS(N metal oxide semiconductor,N型金属氧化物半导体)同时打开形成的瞬间短路电流,短路电流功耗在寄存器发生翻转时产生,因此开关功耗和短路电流功耗统称为动态功耗;第3项是漏电电流功耗,也称为静态功耗,其中Ileakage表示漏电电流.由式(2)可知,时钟频率是动态功耗的主要影响因素,降低时钟频率、关断时钟可有效的降低动态功耗.在系统级芯片中通常采用时钟管理单元实现时钟管理:针对不同模块提供特定频率的时钟,针对功能需求开启/关断时钟.

寄存器级功耗优化主要体现在对工作时钟的管理上.通过对不同层次、不同功能的模块时钟进行精细管理,达到对系统功耗进行优化的目的. WIA-PA系统级芯片包含3个时钟源,其中有2个外部输入时钟,分别为32 MHz外部时钟(CLK_32M)和32 kHz外部时钟(CLK_32K);1个内部32 kHz RC时钟(CLK_RC32K).针对部分模块,还需要额外的输入时钟,如用于定时器的TIM0_EXCLK、TIM1_EXCLK,用于异步通信串口的通信时钟UART0_EXCLK、UART1_EXCLK等.对于每个时钟,都包括使能控制,当使能控制无效时,除了不输出时钟,时钟自身也应进入低功耗状态.

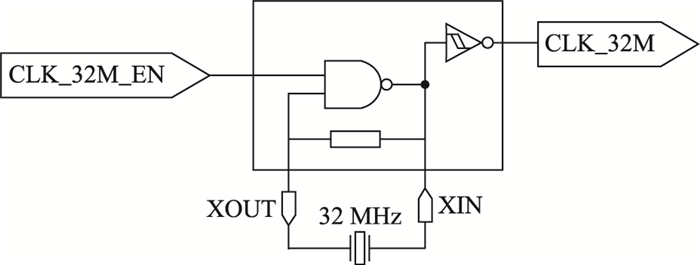

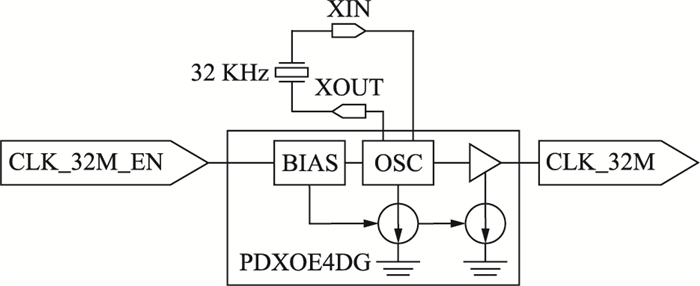

CLK_32M采用外部晶体输入,其电路如图 2所示,由内部晶振电路和外部晶体两部分组成. 32 MHz晶体输入电路受CLK_32M_EN端口控制,当控制信号无效时,CLK_32M端口无时钟输出且时钟电路保持低功耗状态. CLK_32M是系统的主时钟源,供给处理器、总线系统DMA、基带等模块使用.

|

| 图 2 MHz晶振时钟输入电路 Figure 2 32 MHz crystal oscillator clock input circuit |

CLK_RC32K同样采用外部晶体输入,其电路如图 3所示,同样由内部晶振电路和外部晶体两部分组成. 32 kHz晶体输入电路受CLK_32K_EN端口控制,当控制信号无效时,CLK_32K端口无时钟输出且时钟电路保持低功耗状态. 32 kHz晶体输入电路的设计静态功耗在1 μA以内,一般作为休眠唤醒定时器使用.

|

| 图 3 32 kHz晶振时钟输入电路 Figure 3 32 kHz crystal oscillator clock input circuit |

32 kHz RC振荡时钟集成在WIA-PA系统级芯片内,受CLK_RC32K_EN端口控制,输出32 kHz时钟. RC振荡器的输出频率精度较低,因此一般只用来供看门狗定时器使用.当CLK_RC32K_EN端口无效时,RC振荡器保持低功耗状态,且不输出时钟.

2.1.2 内部生成时钟WIA-PA系统级芯片内部依据低功耗要求,对不同的模块设计了不同的工作时钟.对内部模块时钟合理控制,可以达到低功耗的要求.工业无线系统级芯片的内部工作时钟如表 4所示.

| 时钟 | 用途 | 时钟源 | 备注 |

| FCLK | 自由运行时钟 | CLK_32M|CLK_32K|CLK_RC32K | 1/2/4/8分频 |

| MCLK | Cortex-M3 | FCLK|CLK_32K|CLK_RC32K | =FCLK |

| HCLK | AHB总线时钟 | FCLK|CLK_32K|CLK_RC32K | =FCLK |

| DCLK | DMA | FCLK|CLK_32K|CLK_RC32K | =FCLK |

| PCLK | APB接口寄存器 | FCLK|CLK_32K|CLK_RC32K | =FCLK |

| RFTXCLK | 射频发送时钟 | CLK_32M | =32 MHz |

| RFTXCLKINV | 射频发送反向时钟 | CLK_32M | =32 MHz |

| RFRXCLK | 射频接收时钟 | CLK_32M | =32 MHz |

| RFRXCLKINV | 射频接收反向时钟 | CLK_32M | =32 MHz |

| TRACECLKIN | TRACE时钟 | FCLK | 2n分频,n=0,…,5 |

| JTCK | JTAG调试模块 | JTCK | |

| STCLK | SysTick定时器 | FCLK|CLK_32K|CLK_RC32K | 2n分频,n=0,…,5 |

| WatchDCLK | 看门狗时钟 | FCLK|CLK_32K|CLK_RC32K | 2n分频,n=0,…,5 |

| SLPCLK | 休眠定时器时钟 | FCLK|CLK_32K|CLK_RC32K | 2n分频,n=0,…,15 |

| TC0CLK | 定时器0时钟 | FCLK|CLK_32K|TIM0_EXCLK | 2n分频,n=0,…,7 |

| TC1CLK | 定时器1时钟 | FCLK|CLK_32K|TIM1_EXCLK | 2n分频,n=0,…,7 |

| SPI0_CLK | SPI0时钟 | FCLK|CLK_32K|CLK_RC32K | 2n分频,n=0,…,7 |

| SPI1_CLK | SPI1时钟 | FCLK|CLK_32K|CLK_RC32K | 2n分频,n=0,…,7 |

| UART0_CLK | UART0时钟 | FCLK|CLK_32K|UART0_EXCLK | 小数分频 |

| UART1_CLK | UART1时钟 | FCLK|CLK_32K|UART1_EXCLK | 小数分频 |

| PMUCLK | 电源管理单元时钟 | CLK_32M|CLK_32K|CLK_RC32K |

WIA-PA系统级芯片所有的时钟都支持关断,不仅限于一般的外设时钟,也包括DMA、Cortex-M3等主设备的工作时钟.对于一般的外设,如UART0,当不工作时,其时钟可被关闭,即UART0只保持静态功耗.对于MCLK,一般在DMA工作或系统处于休眠状态时,可将其关闭;当DMA传输完成后,或有唤醒事件时,通过唤醒电路,即可自动打开MCLK,Cortex-M3重新进入活动状态.

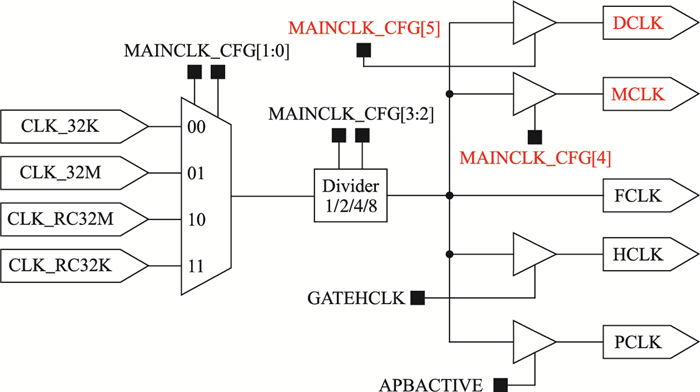

表 4描述内部时钟的来源,如FCLK,自由运行时钟,其时钟源可以是任意3个外部时钟之一,并且支持分频操作. Cortex-M3、DMA、AHB总线、外设等时钟均可由FCLK提供.对于数字系统,频率降低可直接带来功耗的降低. FCLK的时钟频率可由系统的负载进行2/4/8分频控制,从而达到降低系统功耗的目的.图 4以DMA控制器时钟DCLK、主控制器时钟MCLK、自由运行时钟FCLK、AHB总线时钟HCLK和APB总线时钟PCLK为例进行说明. DCLK等时钟首先可以选择不同的时钟源作为时钟输入,选择信号由MAINCLK_CFG[1:0]信号提供;然后可以在MAINCLK_CFG[3:2]的作用下进行1分频;最后可以对每个时钟进行开启或关断控制.图 4中的时钟选择、控制等信号一般都源自寄存器输出或电源管理单元输出.在实际应用中,不同的配置可以生成为不同的时钟输出状态,达到了降低功耗的目的.

|

| 图 4 DCLK/MCLK时钟生成关系图 Figure 4 Relation diagram of the DCLK/MCLK clock generation |

典型的系统级芯片数字部分电源由外部核心电源和I/O电源两部分组成,这两个部分电源电压相等,可统一称为芯片外部电源.随着集成电路生产工艺从亚微米级发展到深亚微米级,集成电路的核心工作电压变得越来越低,核心工作电压一般低于芯片外部电源电压,因此电压转换器件已经成为数字集成电路的必要组件.近年来电压转换器多采用低压差线性稳压器(low dropout regulator,LDO)实现. LDO的设计分为2个方向:一个方向是增大驱动能力,另一方向是降低静态功耗.驱动能力大的LDO静态电流偏大,适合在数字系统工作时使用;静态功耗低的LDO驱动能力弱,适合在数字系统体眠时使用.数字系统在工作、休眠状态下选用合适的LDO可以有效的降低功耗.

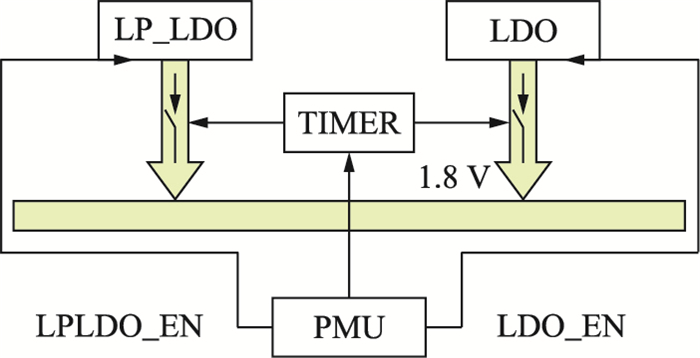

WIA-PA系统级芯片的数字系统集成了2个线性稳压器(LDO),分别为正常LDO和低功耗LDO(LP_LDO). LDO的特点是驱动能力强,但静态电流偏大,一般用于系统在工作时使用.本设计中LDO的最大驱动电流为150 mA,静态电流为120 μA. LP_LDO的特点是驱动能力相对较弱,但静态电流很小,一般用于休眠模式.本设计中采用的LP_LDO最大驱动电流为60 μA,静态电流最大为3 μA. LDO和LP_LDO在WIA-PA系统级芯片内部的切换示意图如图 5所示. LDO和LP_LDO各自受使能信号LDO_EN和LPLDO_EN控制,控制信号由电源管理单元(PMU)生成. LDO的启动时间为110 μs,因此在由LP_LDO切换到LDO时需要进行延时控制,此功能由定时器TIMER实现. LP_LDO由于静态电流较小,在本设计中保持常开状态,实际并不关闭.

|

| 图 5 LDO/LP_LDO切换示意图 Figure 5 Schematic diagram of LDO/LP_LDO switching |

硬件加速器是指实现常用功能的硬件模块,采用硬件加速器替代通用处理器资源实现特定功能,可以降低系统功耗和系统响应时间.硬件加速器的缺点是增加了系统级芯片的面积,在设计过程中也需要加以考虑. WIA-PA标准协议栈是WIA-PA系统级芯片的核心功能,是使用较频繁的功能,因此WIA-PA系统级芯片设计了符合WIA-PA标准的硬件加速器.

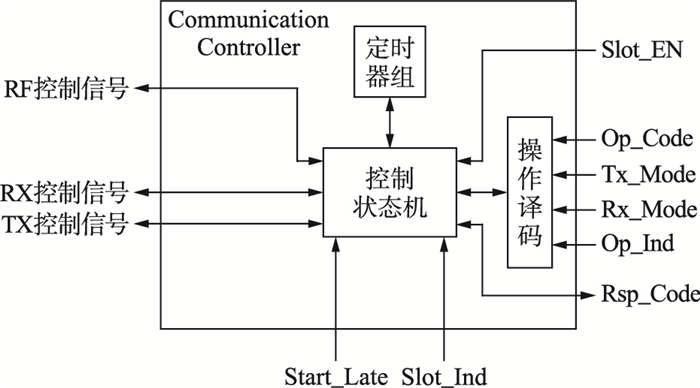

硬件加速器的总体框图如图 6所示,包括定时器组、操作译码和控制状态机等模块. MAC硬件状态机采用定时器组实现.定时器组共包括12个定时器,计时单位为1 μs,用于对时隙内等待、射频发射准备、射频发射、超时等时间进行定时.定时器组对WIA-PA标准时隙内各阶段定时,生成的定时溢出信号传递给控制状态机.然后控制状态机根据定时器溢出信号,来控制本定时器的停止和下一个定时器的启动,控制射频打开或关闭,直到本时隙数据发送或接收完成.由于定时器组和控制状态机的存在,所以在数据发送和接收的过程中并不需要处理器的参与,处理器只需要根据WIA-PA标准规定和实际应用要求来配置定时器组各定时器的计数值,启动收发. WIA-PA硬件加速器的采用降低了系统整体功耗,减少了处理器中断次数,增加了定时精度.

|

| 图 6 WIA-PA硬件加速器框图 Figure 6 Block diagram of WIA-PA hardware accelerator |

WIA-PA系统级芯片内置2个LDO、3个时钟源及大约20个内部生成时钟,主要功能模块包括处理器、2.4 GHz射频、WIA-PA硬件加速器、DMA和外设等.根据WIA-PA标准的工作特点,针对不同工作场景,选择不同LDO和时钟源配置,采用不同工作模式,达到功耗优化目的. WIA-PA系统级芯片分为4个模式,分别为工作模式、休眠模式、深度休眠模式1和深度休眠模式2. WIA-PA系统级芯片在各模式下的LDO、时钟等模块的开关情况如表 5如示.

| 模式 | LP_LDO | LDO | 32M OSC | 32K OSC | MCU | DMA | 外设 |

| 工作模式 | Y | Y | Y | Y | Y | O | O |

| 休眠模式 | Y | Y | O | Y | O | O | O |

| 深度休眠模式1 | Y | X | X | X | X | O | O |

| 深度休眠模式2 | Y | X | X | X | X | X | X |

| 注:Y:活动状态;X:休眠状态;O:状态可选. | |||||||

WIA-PA系统级芯片在工作模式下,由LDO供电,系统时钟为32 MHz,MCU处于活动状态,DMA、外设可根据需要打开或关闭.在工作模式下,芯片的功耗最高.在休眠模式下供电由LDO提供,系统时钟由32 MHz时钟提供,MCU处于休眠状态,DMA和外设根据需要为可选活动状态.休眠模式可快速的切换到工作模式,休眠模式较工作模式节省了MCU部分的功耗.根据应用不同,休眠模式较工作模式功耗可降低30%~80%.在深度休眠模式1下,系统供电由LP_LDO提供,系统时钟由32 KHz时钟提供,LDO和32 MHz时钟关闭,MCU关闭,DMA及外设为可选状态.深度休眠模式1下一般休眠定时器为活动状态,可通过休眠定时器超时中断唤醒系统进入到工作模式,系统功耗可达到μA级.在深度休眠模式2下,系统供电为LP_LDO,其余模块全部为关闭状态.在此模式下功耗达到最低状态,只能通过I/O中断唤醒系统.

当WIA-PA系统级芯片运行WIA-PA协议时,在超帧的非工作时隙期间,芯片处于深度休眠模式1,此时休眠定时器为活动状态,当到达工作时隙时,休眠定时超时,唤醒系统切换到工作模式.在工作时隙的射频收发阶段,芯片处于休眠模式,DMA、外设中的基带、WIA-PA硬件加速器处于活动状态,MCU关闭.当WIA-PA硬件加速器完成协议报文交互处理时,生成中断,唤醒系统切换到工作模式.在工作时隙完成射频收发后,芯片切换到工作模式,在完成射频收发数据处理后,芯片重新进入到深度休眠模式1.深度休眠模式2一般用于在WIA-PA设备出厂时使用;投入使用时,通过I/O可唤醒芯片进入工作模式.

2.5 电源管理单元WIA-PA系统级芯片集成电源管理单元,用于接受休眠、唤醒请求,实现芯片在工作、休眠等模式下的切换.电源管理单元可以对影响功耗的LDO、时钟等资源进行全面的、合理的管理,使芯片达到最优的功耗水平.电源管理单元包括两套配置寄存器组,分别用于存储系统级芯片工作模式下和休眠模式下的LDO选择、时钟配置等信息.电源管理单元的休眠请求由MCU生成,请求类型分别为休眠请求和深度休眠请求.休眠请求为SLEEPING信号,深度休眠请求为SLEEPDEEP信号.电源管理单元的唤醒请求有2类来源:第1类是各种外设的中断信号,第2类是由芯片外部管脚引入的I/O信号.为了实现WIA-PA系统级芯片在无工作时钟状态下由休眠模式切换到工作模式,唤醒模块中使用了部分异步工作电路.

电源管理单元并不是严格的按照休眠请求类型的不同进入到对应的休眠模式,还需要考虑休眠模式下寄存器组的配置.当休眠寄存器组中32 MHz时钟为打开状态时,即使MCU发送深度休眠请求,芯片也只会进入休眠模式,而不会进入深度休眠模式.因为进入深度休眠模式,LDO将切换为LP_LDO,LP_LDO驱动能力弱,无法满足32 MHz时钟工作,有可能导致芯片部分电路的失效.

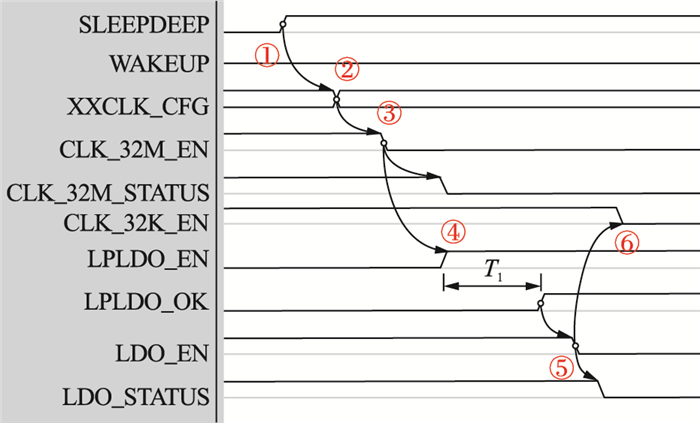

当电源管理单元进行休眠、唤醒切换时,需要充分考虑LDO、时钟等模块的工作特性,按照合理的顺序进行打开或关闭操作,避免因错误的流程导致休眠、唤醒失败.图 6是休眠过程时序图,LDO、时钟等切换过程在图中使用圆圈数字标出.在休眠过程中,第1步是响应MCU生成的SLEEPDEEP信号;第2步是读取休眠寄存器组中的时钟控制信号;第3步关闭32 MHz时钟;第4步打开LP_LDO;第5步为经过T1延时后,LP_LDO工作稳定,关闭LDO,并输出LDO切换状态;第6步为可选步骤,在进入深度休眠模式2时执行,关闭32 kHz时钟.图 7中的T1表示LP_LDO的启动时间.

|

| 图 7 休眠过程时序 Figure 7 Sleep process timing |

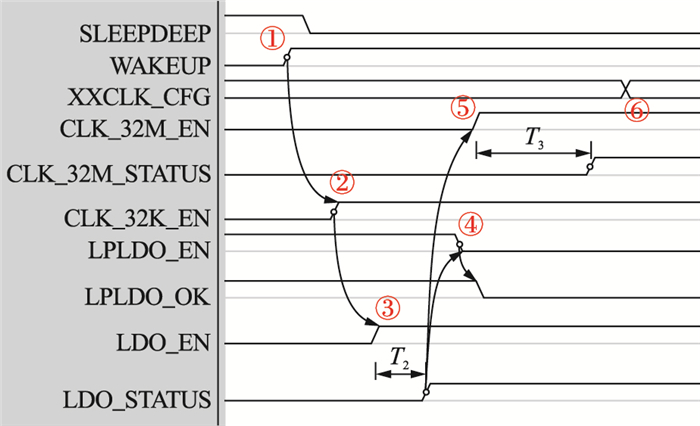

图 8是唤醒过程时序图,同休眠过程时序图中一致,LDO、时钟等切换过程在图中使用圆圈数字标出.在唤醒过程中,第1步是响应唤醒单元生成的WAKEUP信号;第2步是打开32 kHz时钟(如果在切换到休眠模式时32 kHz开启则忽略此步骤);第3步是打开LDO;第4步为经过T2延时后,LDO工作稳定,关闭LP_LDO,并输出LDO切换状态;第5步为打开32 MHz时钟;第6步是经过T3时间延时后,32 MHz恢复工作,根据工作寄存器组中的时钟控制,恢复各模块的工作时钟.图 7中的T2表示LDO的启动时间,T3表示32 MHz时钟的启动时间.

|

| 图 8 唤醒过程时序 Figure 8 Wakeup process timing |

除了系统结构、寄存器优化、电源管理等方面,代工厂提供的先进工艺,对功耗的降低也发挥了极大的作用.为了实现功耗的最优化,特别是静态功耗的优化,WIA-PA系统级芯片分别使用中芯国际(Semiconductor Manufacturing International Corporation,SIMC)0.18 μm工艺(SMIC018)、台积电(Taiwan Semiconductor Manufacturing Company,TSMC)0.18 μm工艺(TSMC018)和TSMC 0.18 μm ULL工艺进行(TSMC018ULL)设计、仿真和功耗分析.经过对EDA工具的功耗分析结果进行对比论证,WIA-PA系统级芯片最终选用TSMC 0.18 μm ULL工艺进行制造.

3 测试与分析 3.1 EDA工具静态功耗对比SMIC 0.18 μm工艺、TSMC 0.18 μm工艺和TSMC 0.18 μm ULL工艺下,对Cortex-M3、DMA和外设进行设计实现及功耗统计,由EDA工具得出的功耗结果如表 6所示,单位为μA.

| 模块 | SMIC018 | TSMC018 | TSMC018_ULL |

| Cortex-M3 | 236 | 98.6 | 2.419 |

| DMA | 87.6 | 43.6 | 1.171 |

| 外设 | 82.83 | 40.728 92 | 1.005 2 |

| 总功耗 | 406.43 | 182.928 92 | 4.595 2 |

由表 6结果可知,采用TSMC018_ULL工艺的WIA-PA系统级芯片的静态功耗较TSMC018及SMIC018工艺具有明显优势,并且本设计中采用的2.4 G射频前端与TSMC018_ULL工艺兼容.所以WIA-PA系统级芯片最终选择TSMC018_ULL工艺制造.

3.2 样片功耗对比测试WIA-PA系统级芯片先后完成2次样片生产过程:第1次主要完成功能验证,版本号为ver 1;第2次在首次功能验证正确的基础上,重点完成低功耗优化设计,版本号为ver 2. WIA-PA系统级芯片第1次流片选用SMIC018工艺,第2次流片选用TSMC018_ULL工艺.经过对两批次样片进行功耗测试,测试结果如表 7所示.

| 功耗 | 第1次样片SMIC018 | 第2次样片TSMC018_ULL |

| 静态功耗 | 267 μA | 1.3 μA |

| 深度休眠功耗 | 522 μA | 7 μA |

| 动态功耗@1 MHz | 1 309 μA | 377 μA |

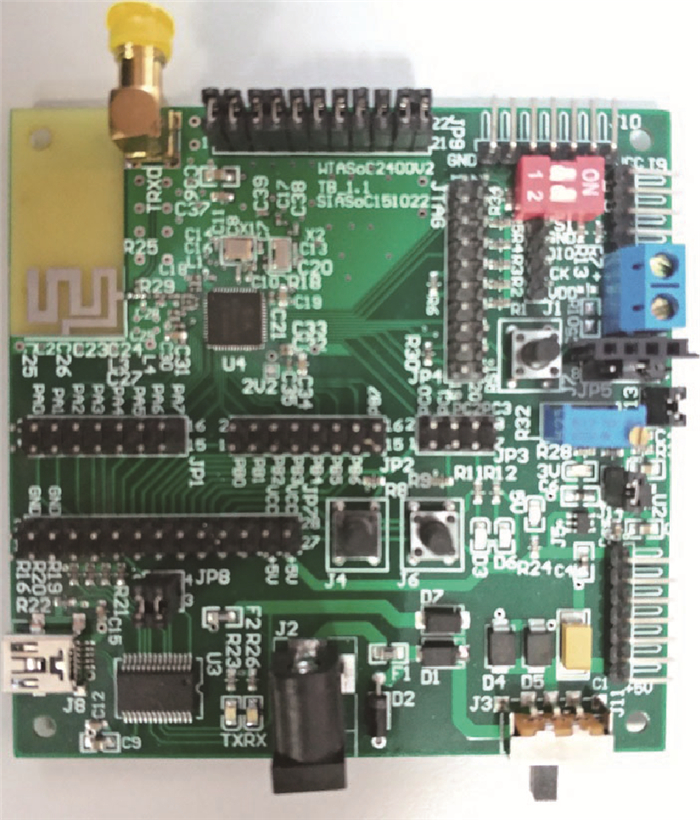

本部分对WIA-PA系统级芯片(TSMC018_ULL)的其它功耗、性能指标进行测试.测试在WIA-PA系统级芯片测试板(图 9)上完成.

|

| 图 9 WIA-PA系统级芯片测试板 Figure 9 WIA-PA SoC test board |

主要的功耗测试指标及测试结果如表 8所示.平均工作电流及深度休眠模式下的工作电流使用7位半高精度万用表测试,瞬间工作电流由电源分析仪测量. WIA-PA系统级芯片的工作电压为2.5 V.

| 测试内容 | 测试结果 |

| 平均工作电流/1 MHz | 377 μA |

| 深度休眠模式1 | 7 μA |

| 深度休眠模式2 | 1.3 μA |

| MCU工作电流 | 13.6 mA |

| 发射电流@0 dbm | 20.9 mA |

| 接收电流 | 14.7 mA |

| 侦听电流 | 6.4 mA |

| Flash页擦除电流 | 15.59 mA |

| Flash编程电流 | 17.28 mA |

| Flash校验电流 | 14.67 mA |

由表 7测试结果进行分析,通过工艺更换及低功耗优化方法的采用,WIA-PA系统级芯片第2次样片较第1次样片的静态功耗降低了99.51%,休眠功耗降低了97.89%,动态功耗降低了71.20%.功耗优化取得了比较理想的结果.表 6测试结果表明,TSMC018工艺较SMIC018工艺在静态功耗上有明显的优势,因此芯片静态功耗和休眠功耗的降低主要来源于此.静态功耗和休眠功耗的降低与LDO/LP_LDO的运用,32 kHz/32 MHz时钟的切换也有一定的关系.芯片动态功耗能够优化主要原因是门控时钟的应用和灵活的工作模式.

采用WIA-PA系统级芯片的WIA-PA现场设备,使用表 8的测量值和表 2中的时间,以WIA-PA系统级芯片功耗占整个现场设备30%进行估算,当使用2 500 mAh的电池时,使用时间为4.23 y,可满足实际的应用需求.

4 结论本文以保证WIA-PA系统级芯片在有限能源的条件下连续长时间工作为目的,通过分析WIA-PA系统级芯片的动态/静态功耗比例,得出功耗优化方向,提出一种综合采用门控时钟、异步电路应用、电源管理模块、系统级优化、工艺制程优选等多种方法相结合的低功耗优化策略. WIA-PA系统级芯片先后完成2次流片,第2次流片实现了本文所提优化策略.通过对两次流片样片进行功耗测试分析对比,动态功耗和静态功耗都有显著的降低,验证了本文所述低功耗优化策略的可行性和有效性.本文所述的优化方法重点对数字系统进行了优化,但对射频前端和其它模拟系统的优化涉及较少,这将是下一步工作的重点.

| [1] |

中华人民共和国国家质量监督检验检疫总局, 中国国家标准化管理委员会.工业无线网络WIA规范, 第1部分: 用于过程自动化的WIA系统结构与通信规范: GB/T 26790.1-2011[S].北京: 中国标准出版社, 2016. General Administrator of Quality Supervision, Inspection and Quarantine of the People's Republic of China, Standardization Administration of the People's Republic of China. Industrial wireless networks WIA specification-Part 1: WIA system architecture and communication specification for process automation (WIA-PA): GB/T 26790.1-2011[S]. Beijing: Standards Press of China, 2016. |

| [2] | IEEE Computer Society. IEEE Standard 802.15.4-2011, Part 15.4: Wireless medium access control (MAC) and physical layer (PHY) Specifications for low rate[S]. New York, NY, USA: IEEE, 2011. |

| [3] |

梁英, 于海斌, 曾鹏, 等.

无线传感器路由协议[J]. 信息与控制, 2005, 34(6): 325–330.

Liang Y, Yu H B, Zeng P. Routing protocols for wireless sensor networks[J]. Information and Control, 2005, 34(6): 325–330. |

| [4] | Hattori T. Challenges for Low-power Embedded SOC's[C]//International Symposium on Vlsi Design, Automation and Test. Piscataway, NJ, USA: IEEE, 2007: 1-4. |

| [5] | El-Razek M A, Abdelhalim M B, Issa H H. Dynamic power reduction of microprocessors for IoT applications[C]//International Conference on Microelectronics. Piscataway, NJ, USA: IEEE, 2017: 297-300. |

| [6] | Chen Y, Lu S, Kim H S, et al. A low power software-defined-radio baseband processor for the Internet of Things[C]//IEEE International Symposium on High PERFORMANCE Computer Architecture. Piscataway, NJ, USA: IEEE, 2016: 40-51. |

| [7] | Cochet M, Clerc S, Naceur M, et al. A 28nm FD-SOI standard cell 0.6-1.2V open-loop frequency multiplier for low power SoC clocking[C]//IEEE International Symposium on Circuits and Systems. Piscataway, NJ, USA: IEEE, 2016: 1206-1209. |

| [8] | Kuroda T, Suzuki K, Mita S, et al. Variable supply-voltage scheme for low-power high-speed CMOS digital design[J]. IEEE Journal of Solid-State Circuits, 1998, 33(3): 454–462. DOI:10.1109/4.661211 |

| [9] | Rajakumar G, Roobert A A, Samuel T S A, et al. Low power VLSI architecture design of BMC, BPSC and PC schemes[J]. Analog Integrated Circuits & Signal Processing, 2017, 93(1): 1–10. |

| [10] | Jamshidi V, Fazeli M. Design of ultra low power current mode logic gates using magnetic cells[J]. AEU-International Journal of Electronics and Communications, 2018, 83: 270–279. DOI:10.1016/j.aeue.2017.09.009 |

| [11] | Kim S, Konar A, Hwang W S, et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals[J]. Nature Communications, 2012, 3(8): 1011. |

| [12] | Lin S H, Chen P Y, Lin Y N. Hardware design of low-power high-throughput sorting unit[J]. IEEE Transactions on Computers, 2017, 66(8): 1383–1395. DOI:10.1109/TC.2017.2672966 |

| [13] |

李贞妮, 李晶皎, 金硕巍.

可靠电压频率岛感知的异步片上网络能耗优化[J]. 信息与控制, 2016, 45(6): 671–676.

Li Z N, Li J J, Jin S W. Reliable voltage-frequency island energy optimization for asynchronous NoC[J]. Information and Control, 2016, 45(6): 671–676. |

| [14] | Tang B Z, Jr S L, Bhave S A, et al. A low power asynchronous GPS baseband processor[C]//IEEE International Symposium on Asynchronous Circuits and Systems. Piscataway, NJ, USA: IEEE, 2012: 33-40. |

| [15] | Reuter J M, Wardensky L L. Providing a capacitor-based power supply to enable backup copying of data from volatile storage to persistent storage: US, US 20100080057 A1[P]. 2010. |

| [16] | Texas Instrument. CC2420 Datasheet[EB/OL].[2017-08-31]. http://www.ti.com.cn/cn/lit/ds/symlink/cc2420.pdf. |

| [17] | Texas Instrument. CC2530 Datasheet[EB/OL].[2017-08-27]. http://www.ti.com.cn/cn/lit/ds/symlink/cc2530.pdf. |

| [18] | Texas Instrument. CC2538 Datasheet[EB/OL].[2017-09-05]. http://www.ti.com/lit/ds/swrs096d/swrs096d.pdf. |

| [19] | NXP Semiconductors. JN516x Datasheet[EB/OL].[2017-09-10]. http://cache.nxp.com/documents/data_sheet/JN516X.pdf. |

| [20] | NXP Semiconductors. MKW2xD Reference Manual[EB/OL].[2017-09-08]. http://cache.nxp.com/assets/documents/data/en/reference-manuals/MKW2xDxxxRM.pdf. |

| [21] | Silicon Lab. EM351/EM357 Datasheet[EB/OL].[2017-09-06]. http://www.silabs.com/documents/public/data-sheets/EM35x.pdf. |

| [22] |

王晋雄, 原义栋, 张海峰.

一种低功耗无电容型LDO的设计[J]. 半导体技术, 2011, 36(4): 316–321.

Wang J X, Yuan Y D, Zhang H F. Design of a low power capacitor-free low dropout regulator[J]. IC Design and Application, 2011, 36(4): 316–321. DOI:10.3969/j.issn.1003-353x.2011.04.015 |

| [23] | Chandrakasan A P, Sheng S, Brodersen R W. Low-power CMOS digital design[J]. IEEE Journal of Solid-State Circuits, 1992, 27(4): 473–484. DOI:10.1109/4.126534 |